Writing a RISC-V Emulator in Rust

NOTE: This project is actively ongoing. Pages are not perfect yet and it possible to change dramatically.

Introduction

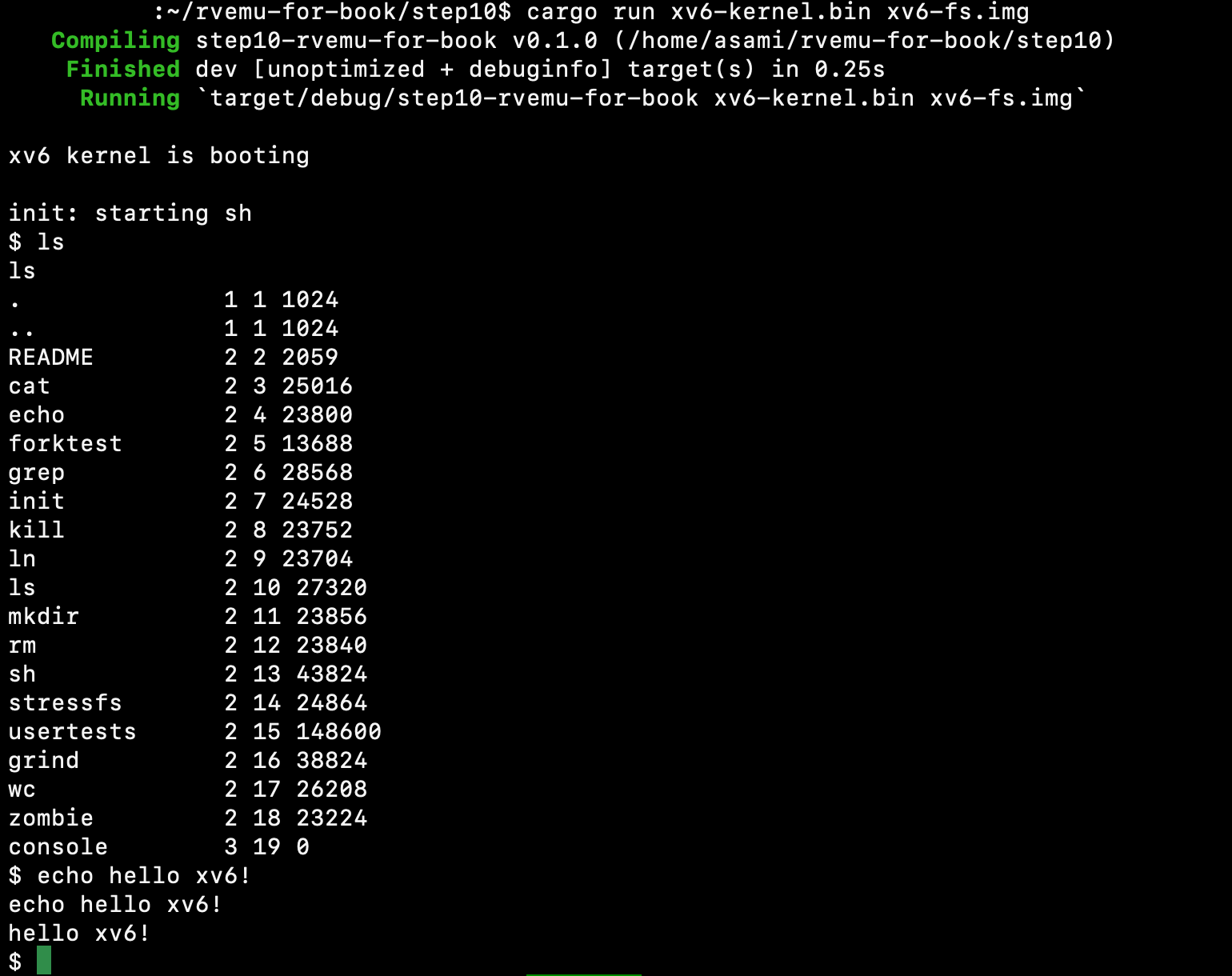

This is the book for writing a 64-bit RISC-V emulator from scratch in Rust. You can run xv6, a simple Unix-like OS, in your emulator once you finish the book.

You'll learn the basic computer architecture such as ISA, previleged architecture, exceptions, interrupts, peripheral devices, and virtual memory system from making an emulator.

The source code used in this book is available at d0iasm/rvemu-for-book.

Chapter 1

Chapter 1 shows all hardward components we need to implement for running xv6.

- CPU with Two Instructions

- Memory and System Bus

- Control and Status Registers

- Privileged Architecture

- Exceptions

- PLIC (a platform-level interrupt controller) and CLINT (a core-local interrupter)

- UART (a universal asynchronous receiver-transmitter)

- Interrupts

- Virtio

- Virtual Memory System

Chapter 2

Chapter 2 shows all ISAs we need to implement for running xv6.

- RV64I Base Integer Instruction Set

- "M" Standard Extension for Integer Multiplication and Division

- "A" Standard Extension for AtomicInstructions

Outcome

Once you read this book and implement the emulator, you will be able to run xv6 in your emulator!

Contact

The author is @d0iasm and please feel free to ask and request anything to me via Twitter or GitHub issues!